Рефераты по рекламе

Рефераты по физике

Рефераты по философии

Рефераты по финансам

Рефераты по химии

Рефераты по хозяйственному праву

Рефераты по цифровым устройствам

Рефераты по экологическому праву

Рефераты по экономико-математическому моделированию

Рефераты по экономической географии

Рефераты по экономической теории

Рефераты по этике

Рефераты по юриспруденции

Рефераты по языковедению

Рефераты по юридическим наукам

Рефераты по истории

Рефераты по компьютерным наукам

Рефераты по медицинским наукам

Рефераты по финансовым наукам

Рефераты по управленческим наукам

Психология и педагогика

Промышленность производство

Биология и химия

Языкознание филология

Издательское дело и полиграфия

Рефераты по краеведению и этнографии

Рефераты по религии и мифологии

Рефераты по медицине

Рефераты по сексологии

Рефераты по информатике программированию

Краткое содержание произведений

Реферат: Конспект лекций по микропроцессорной технике

Реферат: Конспект лекций по микропроцессорной технике

КОНСПЕКТ ЛЕКЦИЙ

по дисциплине «Микропроцессорная техника»

Микропроцессорные и программные средства автоматизации.

Микропроцессорный комплект

Серии К1810

Состав: К1810ВМ86 – центральный процессор (16 бит)

ВМ88 – центральный процессор с восьмибитной шиной данных;

ВМ87 – арифметический сопроцессор;

ВМ59 – процессор ввода/вывода;

ГР84 – генератор тактовых импульсов;

ВГ88 – контроллер системной шины;

ВБ89 – арбитр системной шины

ВТ02 – контроллер для подключения динамической памяти объемом

16 Кбайт

ВТ03 - контроллер для подключения динамической памяти объемом

64 Кбайт

ВН54 – интервальный таймер

ВТ37 – контроллер прямого доступа к памяти

ВН59 – программируемый контроллер прерываний

ИР86/87 – шинные формирователи (с инверсией / без инверсии)

ИР82/83 - регистры-защелки (с инверсией / без инверсии)

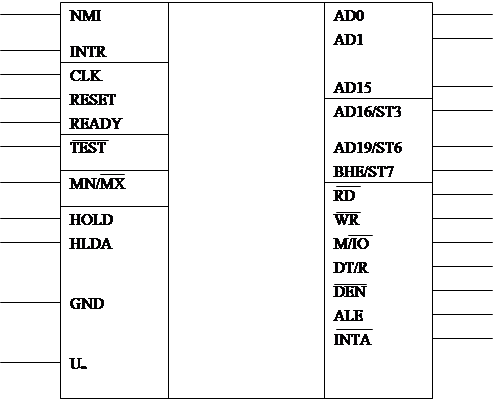

Микросхема К1810ВМ86 (Intel 8086).

Шестнадцатиразрядный однокристальный МП выполняющий около 2 млн. операций в секунду. Синхронизируется тактовой частотой 25 МГЦ.

Имеет 20-ти разрядную шину адреса, что позволяет обеспечить прямую адресацию 1 Мбайт внешней памяти. Область адресного пространства памяти разбита на сегменты по 64 Кб. Такая организация памяти обеспечивает удобный механизм вычисления физических адресов . ША и ШД мультиплексированы. При организации вычислительных систем их нужно разделить (регистры-защелки). МП может обращаться как к памяти, так и к внешним устройствам.

При обращении к внешним устройствам используются 16 младших линий ША. Следовательно можно подключить 64 К 8-битных внешних устройств, либо 32 К 16-ти разрядных. МП имеет многоуровневую систему прерываний: 256 векторов прерываний. Данный МП является дальнейшим совершенствованием К580ВМ80. Система команд сходна, но более расширена. Программное обеспечение легко переводится с одного МП на другой.

Функциональная схема:

См. рис.

В первый такт обмена на AD0-15 устанавливаются младшие 16 бит адреса памяти или адрес внешнего устройства, сопровождается эта информация сигналом ALE. Во втором такте обмена выставляются данные, которые сопровожда-

ются сигналом DEN. ALE и DEN управляют регистрами-защелками. AD16/ST3-AD19/ST6 – мультиплексированные линии адреса состояния.

В первый такт обмена выдается 4 старших разряда адреса памяти, а при обращении к внешнему устройству – нули. Во втором такте выдаются сигналы состояния МП, причем сигналы ST3-ST4 определяют сегментный регистр участвующий в формировании физического адреса.

| ST3 | ST4 | Рег. |

|

0 1 0 1 |

0 0 1 1 |

SS CS DS |

Сегментные регистры. Участвуют в формиро- вании физического адреса.

![]() ST5

– дублирует состояние флага разрешения прерываний.

ST5

– дублирует состояние флага разрешения прерываний.

BHE – разрешение старшего байта. Работает совместно с сигналом А0, обеспечивая механизм передачи информации по ШД.

|

|

A0 | Вид передачи данных |

|

0 0 1 1 |

0 1 0 1 |

Передается 16-ти битное слово Передается старший байт AD8-AD15 Передается младший байт AD0-AD7 Нет обращения |

![]()

|

|

|

|

![]() WR –

сигнал записи.

WR –

сигнал записи.

![]() M/IO – обращение к памяти или внешним

устройствам.

M/IO – обращение к памяти или внешним

устройствам.

![]() DT/R – направление передачи

информации:

DT/R – направление передачи

информации:

«1» - в МП; «0» - из МП.

INTA, INTR – запрос на маскируемое прерывание (INTA – подтверждение прерывания).

NMI – запрос на немаскируемое прерывание.

HOLD – запрос на переход в режим прямого доступа к памяти.

HLDA – подтверждение захвата шины.

![]() TEST

– проверочный вход, используется в команде WAIT для

организации холостых тактов: «1» - МП выполняет «0», с периодичностью 5 Т

проверяет состояние этого сигнала.

TEST

– проверочный вход, используется в команде WAIT для

организации холостых тактов: «1» - МП выполняет «0», с периодичностью 5 Т

проверяет состояние этого сигнала.

MN/MX – минимальный / максимальный режимы, определяющие конфигурацию вычислительной системы. MN- ограничение объема памяти и т.д.

Архитектура МП.

МП содержит в своем составе 14 регистров общего назначения.

AX=AH+AL

BX=BH+BL

CX=CH+CL

DX=DH+DL

Все остальные регистры общего назначения являются неделимыми:

![]()

![]() SP

используются при обращениях к стеку для хранения

SP

используются при обращениях к стеку для хранения

BP адресной информации

SI при обращении к памяти или внешнему устройству

DI

Сегментные регистры:

CS – определят начальный адрес сегмента кода в котором хранится программа;

SS – хранит начальный адрес сегмента стека;

DS – начальный адрес сегмента данных;

ES – начальный адрес дополнительного сегмента под данные;

IP – хранит смещение очередной команды переданной для выполнения.

DA=CS+IP

F- регистр флагов

| 0F | DF | IF | SF | ZF | AF | PF | CF |

AD15 AD0

CF – флаг переноса, фиксирует возникновение переноса при сложении или заеме при вычитании, а также выдвижение старшего байта при операциях сдвига;

PF- флаг четности, фиксирует четное число;

AF – флаг вспомогательного переноса, фиксирует перенос или заем из разряда D4 в D3 при операции сложения и из D3 в D4 при вычитании. Используется при преобразовании кодов из двоичного в двоично-десятичный и наоборот;

ZF – флаг нуля, сигнализирует о получении нулевого результата;

SF – флаг знака, дублирует состояние старшего бита результата операции;

OF – флаг переполнения разрядной сетки, сигнализирует о потере старшего бита при сложении.

Названные 6 флагов сигнализируют о результатах арифметических операций. Оставшиеся 3 флага относятся к флагам управления:

DF – флаг направления обработки команд программы, «0» -выполняется команда от меньших адресов к большим.

IF – флаг разрешения прерываний, если он установлен, то процессор реагирует на запросы прерывания по входу INTR;

TF – флаг трассировки, «1» - МП выполняет команды программы в пошаговом режиме.

В состав МП входит устройство управления, которое дешифрует команды и обеспечивает соответствующие управляющие сигналы. Имеется регистр – очередь команд объемом 6 байт в который загружается очередная команда предназначенная для выполнения. Буфер шины адреса – данных представляет собой 16 двунаправленных усилителей, обеспечивающих номинальную нагрузочную способность шины. Буфер адреса состоит из 4-х двунаправленных усилителей выполняющих аналогичную функцию. Сумматор адресов служит для вычисления физических адресов ячеек памяти. АЛУ – 16-ти разрядное.

Сегментация памяти и вычисление адресов.

Память в ЭВМ на базе К1810ВМ86 организуется как одномерный массив байтов, каждый из которых имеет свой 20-разрядный физический адрес(00000-FFFFF).

Порядок размещения данных в памяти обычный: слово занимает 2 соседние ячейки памяти, причем первым идет младший байт слова, а вторым старший. Физическим адресом слова считается адрес младшего байта слова.

20-ти битный физический адрес ячейки памяти содержится в объекте: сегмент + смещение. Причем на сегмент и на смещение отводится по 2 байта. Следовательно полный физический адрес размещается в 4-х ячейках памяти.

![]() 00002 смещение

00002 смещение

![]() 00003

00003

00004 сегмент

00005

Физическим адресом этого модуля считается адрес младшего байта смещения.

Все пространство памяти объемом 1М разбито на сегменты по 64 К (16 сегментов). Каждому сегменту программой задается его начальный адрес который заносится в сегментные регистры (CS,SS,DS,ES).Такая организация вычислений 20-ти разрядного фактического адреса обусловлена тем, что МП является 16-ти разрядным и все вычислительные операции должны выполняться словами.

Механизм вычисления фактического адреса следующий: содержимое сегментного регистра сдвигается на 4 бита влево. К содержимому смещения присваивается 4 нуля слева.

Сегмент смещение

15 0

| A | B | C | D | 1 | 2 | 3 | 4 |

19 0

19 0

| A | B | C | D | 0 |

+

19 0

| 0 | 1 | 2 | 3 | 4 |

![]()

![]()

| A | C | F | 0 | 4 |

При суммировании может возникать перенос из разряда A19 в A20. Этот перенос игнорируется. Аналогичную кольцевую организацию имеет каждый сегмент. При выборке команда: CS +IP = ФА команды. При обращении к стеку: SS +SP =ФА стека.

Обращение к данным может производиться из любого сегментного регистра: DS (SS,CS,ES) +EA = ФА данных. EA – эффективный адрес, константа, указанная в программе.

К данным можно обратиться через индексные регистры SI и DI; причем индексный регистр хранит смещение на адрес ячейки памяти, откуда данные можно извлечь. А DI хранит смещение на адрес ячейки памяти, куда данные можно направить: DS(SS,CS,ES) +SI=ФА данных; ES+DI =ФА данных. Обращение через регистр BX: ES(CS,SS,DS)+BX= ФА данных. Такая модульная организация памяти посегментно позволяет писать программы в виде отдельных модулей.

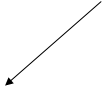

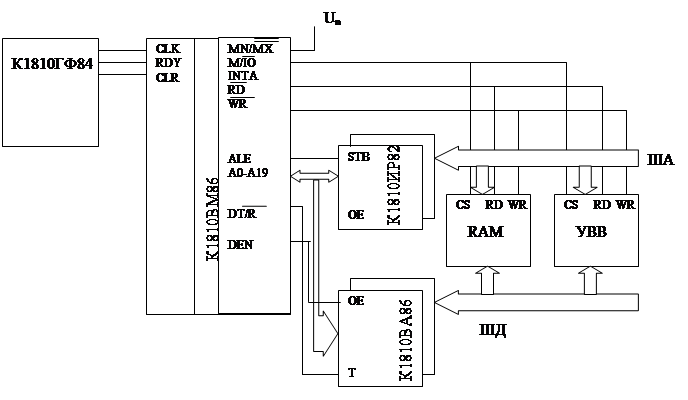

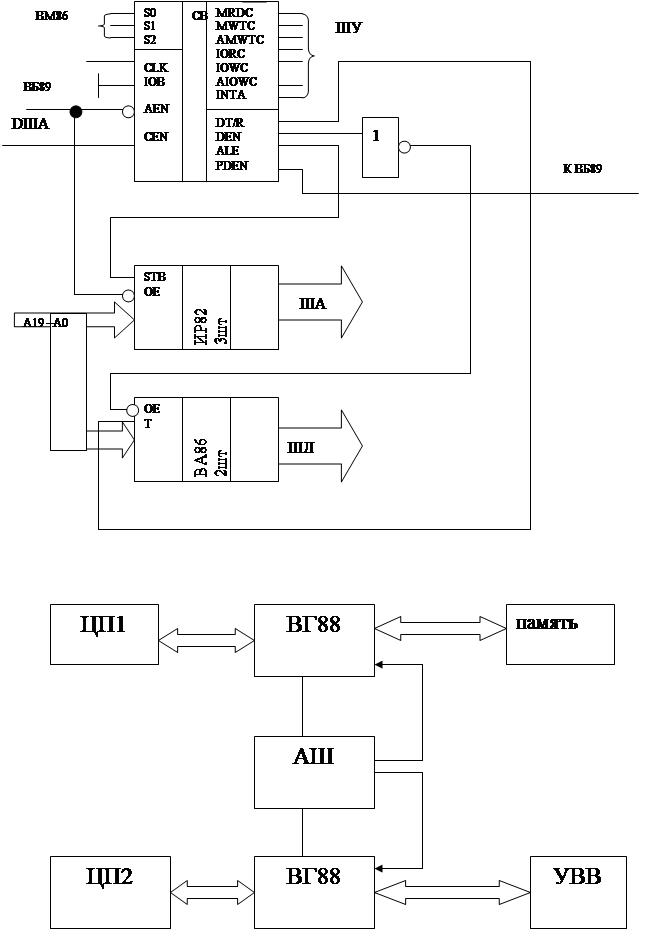

Структурная схема на основе К1810.

При организации вычислительной машины нужно решить следующие задачи:

1) разделить адресные сигналы и сигналы данных;

2) сформировать необходимые управляющие сигналы.

Первая задача решается с помощью буферных регистров К1810ИР82 и шинных формирователей К1810ВА86(87). Вторая задача несколько сложнее и зависит от сложности решаемых задач разрабатываемой микропроцессорной системы. Сложность задачи определяет нужные объемы памяти и количество устройств ввода / вывода. Поэтому МП К1810ВМ86 может работать в двух режимах: минимальный и максимальный. Минимальный позволяет организовывать вычислительные и управляющие системы, имеющие ограниченные объемы памяти и малое количество внешних устройств.

Структурная схема в минимальном режиме

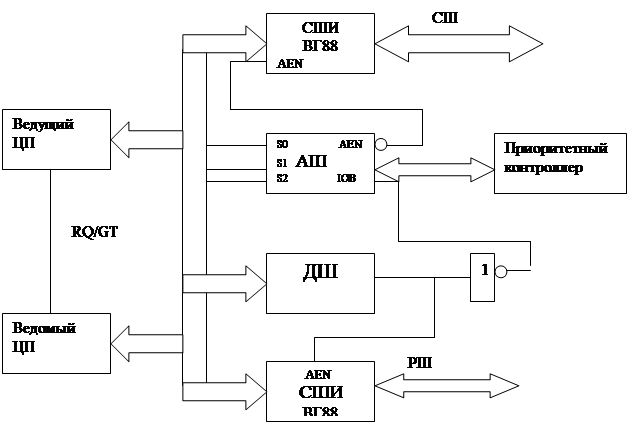

Структурная схема в максимальном режиме.

Функциональные возможности комплекта К1810 позволяют организовать многопроцессорное вычисление системы. Задачу согласования многопроцессорной системы решает арбитр шин К1810ВБ89.

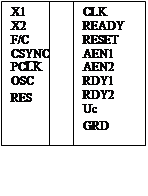

Микросхема К1810ГФ84.

X1,X2 – для подключения

кварцевого резо-

X1,X2 – для подключения

кварцевого резо-

![]() натора

натора

F/C – вход выбора источника тактовой ча-

стоты:

«1» - от собственного задающего генера-

тора

«0» - от внешних сигналов синхронизации

PCLK – выход управления переферией.

OSC – выход внешнего задающего генератора

RES – вход сигнала сброса

CLK – выход ГТИ для управления памятью

READY – выход готовности генератора

RESET – сигнал системного сброса

AEN1,AEN2 – выходы разрешения адресации для сигналов готовности (RDY1, RDY2)

Предназначен для управления ЦМП, памятью, внешними устройствами, контроллером системной шины и арбитром шин. Функционально состоит из генератора тактовой частоты, делителя частоты на 2 и 3 и схемы управления этими устройствами.

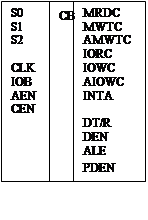

Контроллер системной шины

К1810ВГ88.

Контроллер

предназначен для работы в составе микропроцессорной системы и обеспечивает подключение

к ней памяти и внешних устройств, Функциональные возможности МС: позволяет организовать

конфигурацию вычислительной системы имеющей 2 магистрали: системная шина и резидентная

шина. К системной шине подключается память, к резидентной – устройства в/в.

Контроллер

предназначен для работы в составе микропроцессорной системы и обеспечивает подключение

к ней памяти и внешних устройств, Функциональные возможности МС: позволяет организовать

конфигурацию вычислительной системы имеющей 2 магистрали: системная шина и резидентная

шина. К системной шине подключается память, к резидентной – устройства в/в.

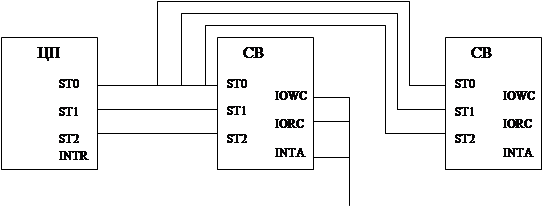

Входы S0-S2 – предназначены для подключения к центральному микропроцессору.

| S0 | S1 | S2 | Режим работы ВМ86 | Командные сигналы ВГ88 |

|

0 1 0 1 0 1 0 1 |

0 0 1 1 0 0 1 1 |

0 0 0 0 1 1 1 1 |

Подтверждение прерывания Ввод данных из устройства в/в Вывод данных в устройство в/в Останов Выборка команды Чтение из памяти Запись в память Пассивное состояние (отключение от системной шины |

INTA IORC IOWC,AIOWC ------- MRDC MRDC MWTC MWTC,AMWC |

Функционирование микросхемы осуществляется на основании следующего кода:

CLK –подключение системного генератора

AEN – строб управления выдачи командных сигналов контроллера (используется в случаях обращения к резидентной шине в/в.)

СEN – сигнал управления при каскадировании ВГ88

IOB - признак обращения к системной шине («0» -системная шина, «1» - резидентная шина)

MRDC – системный сигнал чтения из памяти

MWTC – системный сигнал записи в память

AMWC – опережающий строб при обращении к памяти

IORC – системный сигнал ввода

IOWC – системный сигнал вывода

AIOWC – опережающий строб

INTA – системный сигнал подтверждения прерывания

DEN - строб сопровождения данных для фиксации в регистры-защелки

ALE – строб сопровождения адреса в регистр-защелку

OT/R – сигнал определяющий направление передачи информации («0» -запись в память; «1»- считывание)

STB – сигнал стробирования адреса

PDEN – используется при каскадировании контроллеров системной шины в микропроцессорные вычислительные системы.

Функциональная схема включения.

Данная функциональная схема используется при работе микропрцессора в

максимальном режиме при организациях многопроцессорных систем.

При обращенях к памяти и внешним устройствам очень сильно отличается по быстродействию. Поскольку многопроцессорные системы организовываются для решения сложных задач, требующих большого быстродействия, то нужно выполнять разделение обращения к внешним устройствам и памяти.

К1810ВБ89

![]()

![]()

|

|

|

CLK – вход для подключения системного генератора.

LOCK – вход запрета освобождения системной шины: «1» - арбитру запрещается освобождать системную шину, не зависимо от его приоритета.

CRQLCR - выход запрета освобождения системной шины если поступил запрос по входу CBRQ.

ANYRQST – вход разрешения освобождения системной шины.

RESB – выбор режима работы системной либо резидентной шины («1» - системная шина; «0» - резидентная шина)

IOB – выбор режима работы при вводе / выводе информации через системную либо резидентную шину («1» - системная шина; «0» - резидентная шина)

AEN – сигнал разрешения доступа к системной шине.

BCLK – сигнал синхронизации системной шины.

BREQ – сигнал запроса системной шины.

BPRN – вход разрешения приоритетного доступа к системной шине

BPRQ – выход приоритетного доступа к системной шине.

BUSY – сигнал занятости шины.

CBRQ – вх/вых общего запроса шин.

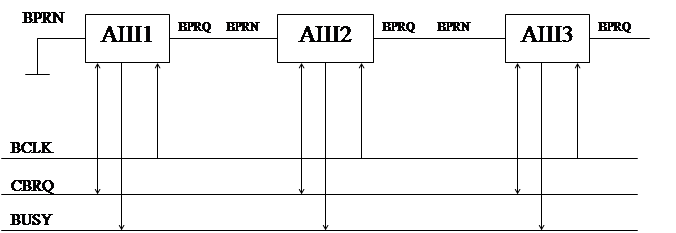

Арбитр шин в многопроцессорной системе может обслуживать 1-2 центральных микропроцессоров. При организации многопроцессорных систем нужно разрабатывать схему приоритетного арбитража. При организации схем приоритетного выбора арбитража используется 3 метода: параллельный; последовательный и циклический арбитраж.

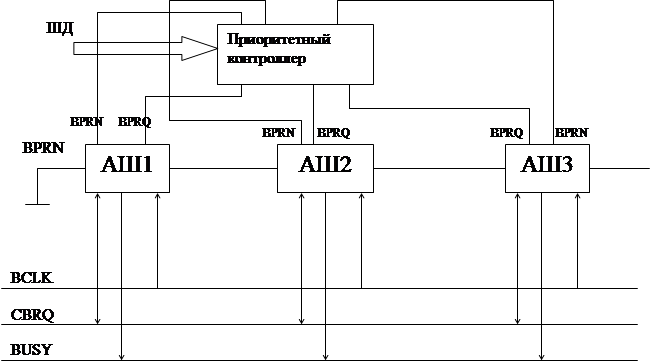

Схема включения арбитража шин при последовательном методе:

При последовательном разрешении приоритетов веса арбитров задаются подключением BPRN с BPRQ. Для схемы, изображенной на рисунке максимальный приоритет будет иметь 1-й АШ, а минимальный – 3-й.

Схема параллельного разрешения приоритетов предполагает использование дополнительного приоритетного контроллера .

В простейшем случае при аппаратном задании весов приоритетов, приоритетный контроллер представляет собой схему, выполненную на логических элементах. Более сложные приоритеты устанавливаются программным путем.

В этом случае приоритетный контроллер имеет связь с шиной данных. В состав приоритетного контроллера входят схемы циклического перераспределения приоритетов .

Арбитр шин может обслуживать 2 микропроцессора:

RQ/GT – обеспечивает доступ к линии связи только одному МП. Выходы другого в этот момент находятся в 3-м состоянии. Дешифратор адреса определяет адрес всей конкретной схемы. Их в многопроцессорной схеме может быть много.

Для подключения к системной или резидентной шине используется контроллер системной шины К1810ВГ88.

Интерфейсы микропроцессорных систем.

Интерфейсы предназначены для организации взаимодействия между микросхемами организующими функциональные модули при построении вычислительной системы. Для организации взаимодействия между вычислительной машиной при организации вычислительных комплексов. Интерфейсы регламентируют правило взаимодействия между всеми функциональными модулями микропроцессорной системы, устанавливают взаимодействие и определяют протоколы и порядок обмена информацией.

Конфигурации интерфейсов разработаны исходя из следующих требований:

1) получение нужного быстродействия и организации стандартного обмена информацией между блоками вычислительной системы независимо от их быстродействия;

2) простота наращивания структуры многопроцессорного комплекса и возможность доступа для диагностики;

3) широкая область применения.

Электрические соединения между выводами микросхем выполняются электрическими связями или линиями. Эти линии сгруппированы по определенному функциональному назначению образуют шину адреса, шину данных и шину управления. Совокупность шин образует магистраль. В зависимости от функционального назначения интерфейсы классифицируются по следующим принципам:

- по способу создания функциональных модулей;

- по способу передачи данных – параллельный, последовательный и последовательно-параллельный ;

- по режиму передачи данных –односторонние, 2-х сторонние, одновременная или поочередная передача.

- по принципу обмена информацией – синхронный и асинхронный.

Интерфейсы в системе MULTIBUS.

Предназначены для организации микропроцессорных модулей. На базе МП К1810 разработаны 2 разновидности интерфейсов – I и II

Интерфейс в системе MULTIBUS состоит из 5-ти магистралей:

- параллельная системная;

- параллельная локальная магистраль LBX;

- многоканальная магистраль в/в MSW;

- локальная в/в SBX;

- управляющая последовательная магистраль – BITBVS;

- Последовательная системная магистраль – SSB;

Параллельная локальная магистраль.

LBX предназначена для подключения к вычислительной системе дополнительных блоков или модулей памяти. С ее помощью можно подключить от 2-х до 5-ти модулей памяти.

Функциональные возможности: может позволить организовать по ней обмен информацией в режиме прямого доступа к памяти. Линии этого интерфейса стандартизованы, образуют 60-ти проводниковый жгут и имеют следущее функциональное назначение:

AB0-AB23 – линия шины адреса;

DB0-DB15 – линия шины данных;

TRAP – разряд проверки четности;

BHEN – разрешение на передачу старшего байта.

ASTB – строб сопровождения информации об адресе;

DSTB – строб сообщения данных;

R/W - сигнал записи / чтения;

XACK- подтверждение передачи в устройство;

LOCK – блокировка магистрали;

SHRA – запрос на переход в режим прямого доступа к памяти;

SMACK- ответ на переход в режим прямого доступа к памяти.

CN0 - линия заземления.

Магистраль работает в режиме чтения/ записи данных. Информация об адресе сопровождается сигналом ASTB, а данных DSTB. Подтверждение приема сопровождается сигналом XACK, обмен информацией происходит в параллельном коде.

Магистраль многоканального в/в MSN.

Предназначена для освобождения системной магистрали от операции в/в при обращении к внешним устройствам. С помощью этой магистрали можно подключить до 16-ти внешних устройств передающих 8 либо 16 разрядные данные со скоростью 8 Мбайт/с. Максимальная длинна этой магистрали до 15 метров. Выполняется в виде стандартного 60-контактного жгута, линии которого имеют следующее функциональное назначение:

AD0-AD15 – мультиплексированная шина адреса/ данных;

GND- линия заземления;

PB,*PB – дифференциальные сигналы дополнения данных до четности.

R/W,*R/W – дифференциальные сигналы чтения /записи.

A/D,*A/D –Дифференциальные сигналы управления адресом/данными;

DRDY,*DRDY – дифференциальные сигналы готовности информации на шине А/D;

AACC – признак приема адреса исполнителем;

DACC – ответ исполнителя при приеме данных;

STQ – завершение процедур обмена;

SRQ – запрос состояния устройства для передачи информации;

RESET – сброс;

SA – готовность передатчика информации.

Магистраль локального в/в SBX.

Предназначена для подключения к одноплатным вычислительным машинам дополнительные платы сопроцессора. Подключается плата с расширенной 2-й системой, арифметикой, графикой. Магистраль имеет 60-ти проводную структуру, линии которой имеют следующее назначение:

MA0-MA2 –младшие разряды адреса, задающие адрес порта при подключении сопроцессора;

MCS0-MCS1 – сигналы выбора микросхем в плате микропроцессора;

MD0-MDF – 16 линий данных;

IORD – сигнал сопровождения адреса при выдаче информации из сопроцессора;

IOWRT – сигнал сопровождения адреса при выдаче информации в сопроцессор;

RESET – сброс линии или начальная установка;

MWAIT – ожидание сигнала сопровождения процедуры обмена сопроцессора;

MDRQT – запрос режима прямого доступа к памяти у ЦП;

MDACK – подтверждение прямого доступа к памяти;

TDMA – сигнал завершения работы каналов прямого доступа к памяти;

MCLK – сигнал синхронизации для сопроцессора;

MPST – признак наличия модуля расширения, сопроцессора.

С помощью магистрали можно подключить 8 сопроцессоров со скоростью передачи информации не более 10 Мбайт /с.

Магистраль связи BITBUS.

Последовательная управляющая магистраль предназначенная для передачи информации в режиме синхронной передачи до 30 метров, в режиме асинхронной передачи до нескольких километров. В режиме синхронной передачи скорость может быть 500 Кбит/с либо 2,4 Мбит/с.

В режиме асинхронной передачи скорость может быть – 62,5 Кбит/с либо 375 Кбит/с.

Магистраль предназначена для регистрации локальных сетей. Физически она представляет собой 9-ти канальный жгут проводов, имеющий функциональное назначение.

DATA,*DATA – дифференцированная сигнальная пара – линия для передачи данных.

DCLK / RTS, *DCLK / RTS – дифференциальная пара – сигнальная, синхронизации управления.

GND, +12D – общая линия управления

ZGND – 3-е состояние

Обмен информацией по этой магистрали выполняется кадрами, которые имеют следующий формат:

Параллельная системная магистраль.

Предназначена для подключения к центральному процессору для подключения устройств (до 20-ти устройств).

Внешние прерывания бывают:

1) маскируемые, поступающие по входу INTR;

2) немаскируемые, поступающие по входу NMI. На запросы на немаскируемые прерывания МП обрабатывает всегда независимо от состояния флага прерывания;

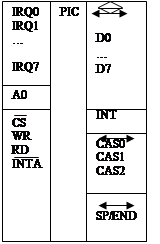

Процедура обслуживания внешних прерываний выполняется с помощью специального контроллера прерываний КР1810ВН59.

|

IRQ0-IRQ7 – запросы на прерывания. Если программируемым путем не произведено перераспределение приоритетов, то IRQ – маскируемый приоритет.

A0 – адрессный вход для подключения младшей линии адреса.

СS – выбор микросхемы.

WR – запись информации в микросхему.

RD – чтение.

INTA – подтверждение прерывания.

D0–D7 – входы данных (для программирования микросхемы). Подключаются к младшему байту шины данных.

INT – вход прерывания.

CAS0-CAS2 – входы для каскадирования микросхем.

Микросхема может работать в режимах программирования и режиме обслуживания переферии. Режим программирования задается CS=0.

Схема подключения контроллера к системной шине.

|

Схема каскадирования.

Схема каскадирования.

Организация запоминающих устройств.

Для запоминания информации в цифровых схемах используется либо триггер, либо конденсатор. В зависимости от типа запоминающего устройства различают память SIMM и DIMM.

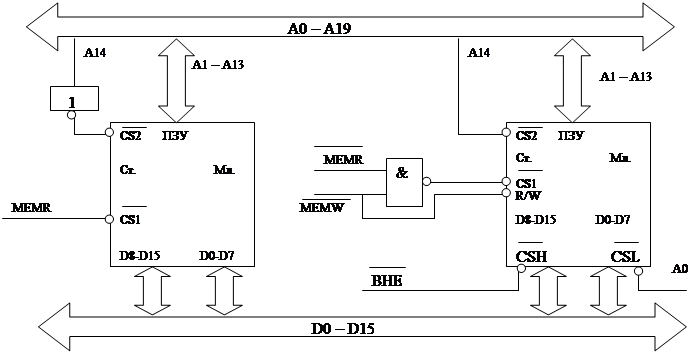

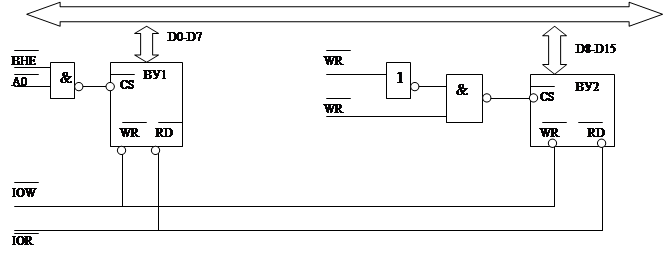

При подключении запоминающего устройства к системной шине нужно организовывать передачу не только слов, но и отдельных файлов. Для реализации этого блоки памяти обычно выполняются в виде 2-х банков. Младший подключают к линиям данных D7-D0 и содержит байты с четными адресами. Для выбора этого банка в микропроцессорной системе используется А0=0. Старший байт D8-D15 – А0=1. При передаче байта данных его нужно переслать в ячейку памяти с четными адресами. В этом случае цикл обмена данными составляет 1 период системной синхронизации. Вид пересылки данных по системной магистрали определяет кроме сигнала А0 еще сигнал BHE. А0 совместно с BHE образуют:

| A0 | BHE | Вид посылки |

|

0 1 |

1 0 |

Мл. байт Ст. байт |

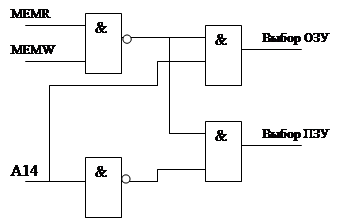

Выработка сигналов А0 и BHE выполняется автоматически под действием управляющей программы. Для упрощения схемы подключения при организации ПЗУ следует учесть тот факт, что при чтении информации из запоминающего устройства на шину данных всегда выставляется 2 байта данных, Селекцию необходимой информации выполняет ЦП и выбирая нужную, помещает ее в свои внутренние регистры. Следовательно сигналы А0 и BHE к ПЗУ можно не подключать. При обращении к ОЗУ для выбора банка данных можно использовать сигналы А0 и BHE. Обращения к ПЗУ стробируется сигналом МЕМR и MEMW.

Схема подключения:

Схема подключения:

Линия А14 используется для выбора блока ОЗУ либо ПЗУ. ПЗУ может быть реализовано на 2-х микросхемах К573РФ4 (4096*16). Следовательно А13 – используется как вход выборки кристаллов каждой микросхемы. ОЗУ – 8 микросхем К537РУ10(2048 *8).

Организация блоков памяти больших объемов.

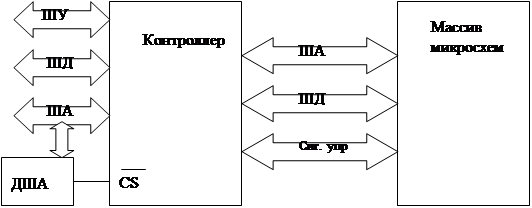

Большие блоки памяти организуются в виде модулей (печатная плата), которых может быть несколько. Каждый модуль может подключаться к системной либо резидентной шине и имеет следующую внутреннюю организацию:

| RAS | CAS | W/R | D | Выход В | Режим работы |

|

1 1 0 0 0 |

1 0 1 0 0 |

0 0 0 0 1 |

0 0 0 0 |

3-е состояние 0 или 1 |

Нет обращения Регенерация микр-мы Запись информации Чтение информации |

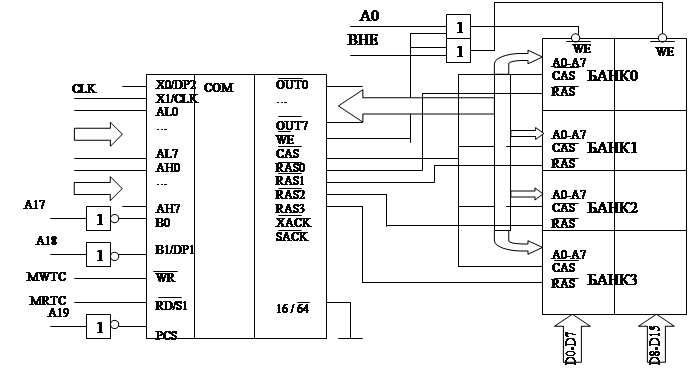

ДША – предусматривается для каждого блока памяти. Контроллер: К1810ВТ02 (ВТ03). Совместно с микропроцессором используются микросхемы динамической ОЗУ серии К565. Запись информации в микросхемы ОЗУ выполняется в соответствии со следующей диаграммой:

1-й такт – записывается код адреса строки, которая стробируется сигналом RAS, во втором такте записывается код адреса столбца сигналом CAS, а также происходит процедура записи/чтения R/W. Такая двухсторонняя процедура записи информации экономит адресные выходы микросхем ОЗУ. Мультиплексирование адресных линий и двухступенчатая процедура обмена позволила сэкономить количество выводов на микросхемах ОЗУ.

Способы дешифрации адреса.

Способ дешифрации адреса зависит от объемов ОЗУ и ПЗУ, количества и типа устройств ввода/вывода. При проектировании микропроцессорной системы используются следующие способы дешифрации адреса:

1) линейный выбор. Самый простой способ, не использующий логику дешифрации адреса. Технически реализуется следующим образом: любая линия ША используется как сигнал выборки кристаллов. Пример реализации:

Способ используется при подключении малых объемов памяти. Недостатком является большая потеря области адресного пространства;

2) дешифрация с помощью логического компаратора. Простой и очень гибкий способ дешифрации адреса. В этом случае логический компаратор устанавливается на каждую печатную плату, с помощью перемычек устанавливается адрес каждой печатной платы. При совпадении кода задаваемого перемычками с кодом установленном на соответствующих адресных линиях, формируется сигнал выборки кристаллов. Технически логический компаратор может быть выполнен на схемах совпадения.

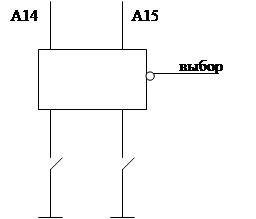

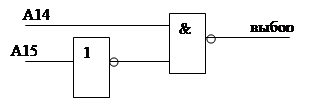

3) дешифрация с помощью комбинаторной логики. В этом случае для формирования сигналов выборки кристалла используется логические элементы:

Сигнал выборки кристалла формируется, если А14=1, а А15=0.

Данная схема позволяет оьратиться по адресам 4000 – 7FFF. Недостатком является жесткая логика.

3) Дешифрация адреса с помощью дешифратора. В этом случае выбирается одна из 2n возможных комбинационных входных сигналов, где n-количество входов, подключенных к дешифратору.

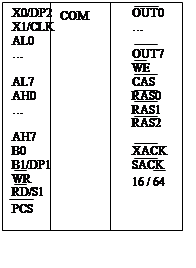

Микросхема К1810ВТ3 – контроллер управления динамической памятью.

X0,X1- входы для подключения кварцевого резонатора для выработки

сигналов регенерации памяти. Либо к X1 можно подключить

CLK. AL0-AL7;

AH0-AH7 – адрессные входы для

выборки ячейки памяти внутри памяти.

X0,X1- входы для подключения кварцевого резонатора для выработки

сигналов регенерации памяти. Либо к X1 можно подключить

CLK. AL0-AL7;

AH0-AH7 – адрессные входы для

выборки ячейки памяти внутри памяти.

WR,RD/S1 – сигналы системной записи/чтения.

B0,B1 – входы дешифратора (выборка банков памяти).

PCS – вход выборки кристалла контроллера.

OUT0-OUT7 – мультиплексированные выходы выбора адрессов строк и столбцов.

WE – сигнал считывания памяти.

CAS – RAS2 – сигналы управления микросхемами динамической памяти.

XACK – ответ памяти на сигналы обращения к ней.

SACK – готовность памяти.

Пример подключения управления динамической памятью объемом 512 Кбайт показан на рисунке:

Обмен информацией с внешними устройствами.

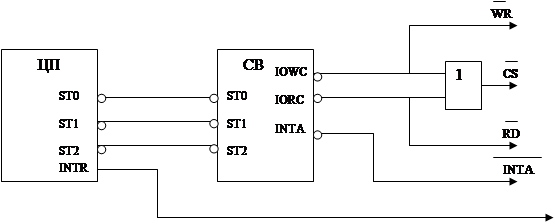

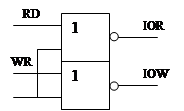

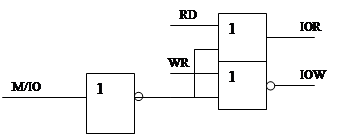

1) организация ввода/вывода. Обмен информацией между микропрцессором и внешними устройствами выполняется 2-мя способами: использование адресного пространства в/в; использование общего с памятью адрессного пространства. Техническая реализация 1-го способа предусматривает разделение всей области адресного пространства на память и адреса внешних устройств. Обмен данными между микропрцессором и внешними устройствами выполняется по коммандам IN и OUT. Для аппаратной идентификации адрессного пространства в/в используется сигнал M/IO=0. При работе микропроцессора в минимальном режиме системные сигналы управления вводом/выводом могут быть получены с помощью логических элементов:

При работе микропроцессора в

максимальном режиме системные комманды ввода/вывода вырабатывает системный

контроллер К1810ВГ88. Комманды ввода/вывода реализуют 2 типа адрессации:

При работе микропроцессора в

максимальном режиме системные комманды ввода/вывода вырабатывает системный

контроллер К1810ВГ88. Комманды ввода/вывода реализуют 2 типа адрессации:

1) прямая адрессация, в этом случае код адресса порта указывается во втором байте комманды. Этот вид адрессации обеспечивает обращение к 256 портам в/в;

2) косвенная адрессация, в этом случае вовтором байте комманды указывается регистр DX и поскольку он 16-ти разрядный, то можно организовать 65536 внешних устройств. При такой адрессации в/в под адрессацию портов отводится один сегмент памяти. При втором способе адрессации внешние устройства находятся в общем адрессном пространстве с памятью. Поэтому в этом случае обращение к ним может быть выполнено как к обычным ячейкам памяти. Длявыполнения операций в/в кроме комманд IN и OUT могут быть использованы любые комманды пересылки. Второй способ имеет большие функциональные возможности. В нем может быть организована с помощью специальных комманд пересылка данных междк ЦП и внешними устройствами, между внешними умтройствами и памятью. Колличество подключаемых внешних устройств до 1Мб.

В прстейшем случае в минимальном режиме для обращения к внешним устройствам могут быть использованы системные сигналы MEMR, MEMW, которые получаются из сигналов МП WR и RD:

При обмене данными МП передает по ШД либо все слово (16 бит), либо младший байт. Чтобы байт был передан за один цикл системной синхронизации нужно, чтобы адресс внешнего устройства был четным. Также внешние устройства должны подключаться к младшему байту ШД. Для идентификации раздельного подключения внешних устройств к младшему либо старшему байту данных используются сигналы А0 и BHE. Состояние этих сигналов указано в таблице(см.ВМ86).

Подключение внешних устройств к системной магистрали.

При подключении внешних устройств возникает проблема согласования 8-ми битной ШД внешнего устройства с 16-ти битной ШД микропроцессора. Данная задача решается 2-мя способами:

1) внешнее устройство подключается либо к старшему, либо к младшему байту ШД. Для идентификации внешнего устройства (CS) используются сигналы A0 и BHE.

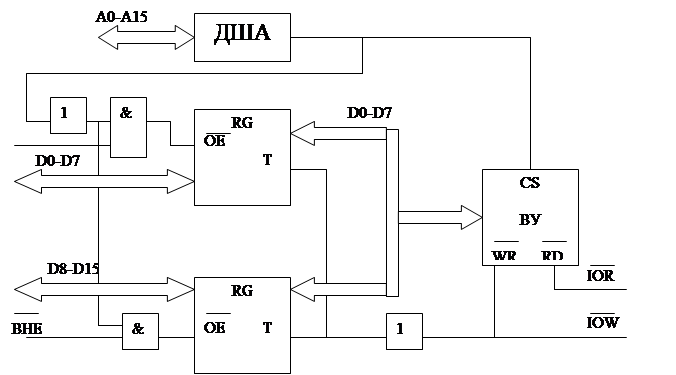

Второй способ заключается в преобразовании 16-ти разрядной шины данных в 8-ми разрядную. Для этой цели можно использовать 2 регистра-защелки (К1810, ИР82/Ир83).

Эта схема включения работает в режиме в/в с отображением на память. Передаваемая и принимаемая информация может распределяться как по четным, иак и по нечетным адресам. Длинна пересылки данных определяют сигналы А0 и BHE.

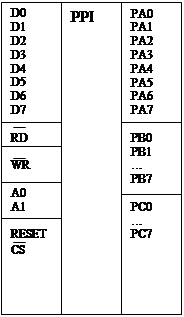

Программируемый парралельный интерфейс.

Микросхемы данного типа не входят в состав конкретных микропроцессор-ных комплектов.

8225

Обычно для обмена данными

используются 8 линий порта А или порта B. Для выраьотки

управляющих сигналов обычно используется порт С. Режим работы схемы

определяется управляющим словом, которое заносится в ее внутренний регистр при

инициализации системы. При этом допускается прграммирование нескольких режимов

работы:

Обычно для обмена данными

используются 8 линий порта А или порта B. Для выраьотки

управляющих сигналов обычно используется порт С. Режим работы схемы

определяется управляющим словом, которое заносится в ее внутренний регистр при

инициализации системы. При этом допускается прграммирование нескольких режимов

работы:

- весь порт работает на вывод информации

- весь порт работает на ввод информации

- отдельные на ввод, отдельные на вывод.

Назначене линий :

D0-D7 - входы для подключения к резидентной или системной шине.

A0,A1 - входы выбора порта

По скольку архитектура центрального процессора 16-ти разрядная, а микросхема порта 8-ми разрядная возможны 2 варианта подключения данной микросхемы. При передаче 8-ми разрядных данных интерфейс подключается к младшему байту шины данных, а центральный процессор программируется на вывод этого байта. Для передачи всего слова нужно использовать 2 контроллера.

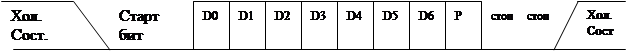

Программируемый последовательный интерфейс.

Последовательный обмен данных регламентируется в стандарте RS232C. Этот стандарт предусматривает для передачи информации 3 линии связи: общая, линия передачи (ВА) и линия приема (ВВ). Протокол обмена данными имеет следующий формат:

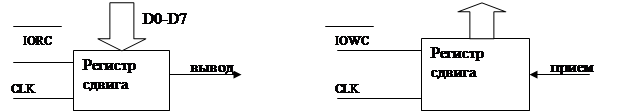

Функционально последовательный интерфейс реализуется на 2-х сдвигающих регистрах:

Последовательный интерфейс может работать в синхронном и асинхронном режиме. Синхронный режим подразумевает работу интерфейса приемника и передатчика под управлением системного генератора.

|

|||

|

|||

|

|

|