Рефераты по рекламе

Рефераты по физике

Рефераты по философии

Рефераты по финансам

Рефераты по химии

Рефераты по хозяйственному праву

Рефераты по цифровым устройствам

Рефераты по экологическому праву

Рефераты по экономико-математическому моделированию

Рефераты по экономической географии

Рефераты по экономической теории

Рефераты по этике

Рефераты по юриспруденции

Рефераты по языковедению

Рефераты по юридическим наукам

Рефераты по истории

Рефераты по компьютерным наукам

Рефераты по медицинским наукам

Рефераты по финансовым наукам

Рефераты по управленческим наукам

Психология и педагогика

Промышленность производство

Биология и химия

Языкознание филология

Издательское дело и полиграфия

Рефераты по краеведению и этнографии

Рефераты по религии и мифологии

Рефераты по медицине

Рефераты по сексологии

Рефераты по информатике программированию

Краткое содержание произведений

Реферат: Устройство синхронизации информационных импульсов, поступающих в произвольные моменты времени, с ближайшим спадом тактового импульса

Реферат: Устройство синхронизации информационных импульсов, поступающих в произвольные моменты времени, с ближайшим спадом тактового импульса

З А Д А Н И Е

на курсовое проектирование

ТЕМА: Устройство синхронизации сигналов

Требования:

- напряжение питания 5в +- 5%

- потребляемая мощность: не более 80 мВт

- время наработки на отказ не менее 500000 час

- частота тактовых импульсов 1 мГГц.

Условия эксплуатации:

- диапазон рабочих температур от -300 С до +400 С;

- перегрузки до 5g;

- одиночные удары с ускорением не более 10g длительностью 0.1-1 мкс;

- вибрация с частотой 10 - 500 Гц и ускорением не более 10g.

Срок эксплуатации 15 лет, наработка за время эксплуатации до 85 тыс. часов.

Дополнительные требования.

Предусмотреть меры обеспечения контроля при изготовлении и эксплуатации

Содержание пояснительной записки.

1. Анализ технического задания

2. Формализация описания конечного автомата (граф автомата, таблицы переходов и выходов)

3. Минимизация памяти абстрактного автомата

4. Выбор способа противогоночного кодирования

5. Противогоночное кодирование состояний автомата

6. Формирование функций выходов и функций возбуждения памяти автомата

7. Минимизация графическим методом функций выходов и функций возбуждения памяти автомата

8. Составление логической схемы устройства

9. Выбор метода обеспечения контролепригодности и преобразование схемы устройства

10. Разработка принципиальной схемы устройства

11. Расчет основных параметров устройства (время переключения, потребляемая мощность, время наработки на отказ)

12. Моделирование работы устройства или составление временной диаграммы его работы, анализ правильности функционирования

13. Оценка степени выполнения задания

Примечание: При проектировании полагать, что очередной информационный импульс на вход устройства не поступает до окончания цикла его работы и возвращения в исходное состояние.

Плакаты и чертежи

1. Принципиальная схема устройства

Конечный автомат должен осуществлять синхронизацию информационных импульсов, поступающих в произвольные моменты времени, с ближайшим спадом тактового импульса, начинающимся после поступления фронта информационного импульса. Длительность формируемого синхронизированного импульса равна периоду следования тактовых импульсов. Максимальная длительность информационного импульса не ограничена

X = {00, 01, 10, 11}

Y = {0, 1}

| ТИ | ИИ | |

| X0 | 0 | 0 |

| X1 | 1 | 0 |

| X2 | 0 | 1 |

| X3 | 1 | 1 |

Таблица переходов δ(q,x)

| q0 | q1 | q2 | q3 | q4 | q5 | |

| X0 | q0 | q1 | q3 | q3 | q0 | q0 |

| X1 | q0 | q2 | q2 | q4 | q4 | q0 |

| X2 | q1 | q1 | q3 | q3 | q5 | q5 |

| X3 | q2 | q2 | q2 | q4 | q4 | q5 |

Таблица выходов λ(q,x)

| q0 | q1 | q2 | q3 | q4 | q5 | |

| X0 | 0 | 0 | 1 | 1 | 1 | 0 |

| X1 | 0 | 0 | 0 | 1 | 0 | 0 |

| X2 | 0 | 0 | 1 | 1 | 0 | 0 |

| X3 | 0 | 0 | 0 | 1 | 1 | 0 |

Минимизация памяти абстрактного автомата

Таблица выходов λ(q,x)

| q0 | q1 | q2 | q3 | q4 | q5 | |

| X0 | 0 | 0 | 1 | 1 | 1 | 0 |

| X1 | 0 | 0 | 0 | 1 | 0 | 0 |

| X2 | 0 | 0 | 1 | 1 | 0 | 0 |

| X3 | 0 | 0 | 0 | 1 | 1 | 0 |

| A0 | A0 | A1 | A2 | A3 | A0 |

A0 = {q0, q1, q5}

A1 = {q2}

A2 = {q3}

A3 = {q4}

| q0 | q1 | q5 | q2 | q3 | q4 | |

| X0 | A0 | A0 | A0 | A2 | A2 | A0 |

| X1 | A0 | A1 | A0 | A1 | A3 | A3 |

| X2 | A0 | A0 | A0 | A2 | A2 | A0 |

| X3 | A1 | A1 | A0 | A1 | A3 | A3 |

| B0 | B1 | B2 | B3 | B4 | B5 |

Таким образом, невозможно минимизировать память абстрактного автомата.

Выбор способа противогоночного кодирования

Существует ряд способов противогоночного кодирования, которые можно разбить на две группы:

1. Методы, позволяющие устранить все состязания. Используется “соседнее кодирование”, когда всем соседним внутренним состояниям приписывают соседние кодовые комбинации, отличающиеся значением только 1 разряда.

В случае использования таких методов уменьшается быстродействие, но зато устраняются все состязания.

2. Методы, устраняющие только критические состязания (состязания при которых в дальнейшей работе автомат не переходит из ошибочных состояний в состояние, предусмотренное алгоритмом функционирования)

Для упрощения схемы и увеличения быстродействия устраняем только критические состязания.

Противогоночное кодирование осуществляется путем развязывания пар переходов.

Две пары двоичных наборов длины “l” – (α,β) и (γ,δ) называются развязанными, если i-ый разряд кода принимает одно значение на паре (α,β) и другое на паре (γ,δ)

Противогоночное кодирование состояний автомата

| M0 | M1 | M2 | M3 |

|

q0, q0 q1, q1 q2, q3 q3, q3 q4, q0 q5, q0 |

q0, q0 q1, q2 q2, q2 q3, q4 q4, q4 q5, q0 |

q0, q1 q1, q1 q2, q3 q3, q3 q4, q5 q5, q5 |

q0, q2 q1, q2 q2, q2 q3, q4 q4, q4 q5, q5 |

|

τ1 |

τ2 |

τ3 |

|

| q0 | 0 | 0 | 0 |

| q1 | 1 | 0 | 0 |

| q2 | 1 | 1 | 0 |

| q3 | 1 | 1 | 1 |

| q4 | 0 | 1 | 1 |

| q5 | 0 | 0 | 1 |

Развязывание пар переходов в массиве М0

| 1 | q0 | q0 | q1 | q1 |

| 0 | 0 | 1 | 1 |

| 3 | q0 | q0 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 2 | Q0 | q0 | q2 | q3 |

| 0 | 0 | 1 | 1 |

| 4 | q1 | q1 | q2 | q3 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 6 | q1 | q1 | q4 | q0 |

| 1 | 1 | 0 | 0 |

| 5 | q0 | q0 | q2 | q3 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 7 | q1 | q1 | q5 | q0 |

| 1 | 1 | 0 | 0 |

| 8 | q2 | q3 | q4 | Q0 |

| 1 | 1 | 0 | 0 |

| 9 | q2 | q3 | q5 | q0 |

| 1 | 1 | 0 | 0 |

| 10 | q3 | q3 | q4 | q0 |

| 1 | 1 | 0 | 0 |

| 11 | q3 | q3 | q5 | q0 |

| 1 | 1 | 0 | 0 |

Развязывание пар переходов в массиве М1

| 1 | q0 | q0 | q1 | q2 |

| 0 | 0 | 1 | 1 |

| 2 | q0 | q0 | q2 | q2 |

| 0 | 0 | 1 | 1 |

| 3 | q0 | q0 | q3 | q4 | |

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 4 | q0 | q0 | q4 | q4 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 5 | q1 | q2 | q3 | q4 | |

| 1 | 1 | 1 | 0 | ||

| 0 | 1 | 1 | 1 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 6 | q1 | q2 | q4 | q4 |

| 1 | 1 | 0 | 0 |

| 7 | q1 | q2 | q5 | q0 |

| 0 | 0 | 1 | 1 |

| 8 | q2 | q2 | q3 | q4 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 1 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 9 | q2 | q2 | q4 | q4 |

| 1 | 1 | 0 | 0 |

| 10 | q2 | Q2 | q5 | q0 |

| 1 | 1 | 0 | 0 |

| 11 | q3 | q4 | q5 | q0 | |

| 1 | 0 | 0 | 0 | ||

| 1 | 1 | 0 | 0 |

τ2 |

| 12 | q4 | q4 | q5 | q0 | |

| 0 | 0 | 0 | 0 | ||

| 1 | 1 | 0 | 0 |

τ2 |

Развязывание пар переходов в массиве М2

| 1 | q0 | q1 | q2 | Q3 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 2 | q0 | q1 | q3 | q3 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 3 | q0 | q1 | q4 | q5 | |

| 0 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 0 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 4 | q0 | q1 | q5 | q5 | |

| 0 | 1 | 0 | 0 | ||

| 0 | 0 | 0 | 0 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 5 | q1 | q1 | q2 | q3 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 6 | q1 | q1 | q3 | q3 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ2 |

| 9 | q2 | q3 | q4 | q5 |

| 1 | 1 | 0 | 0 |

| 7 | q1 | q1 | q4 | q5 |

| 1 | 1 | 0 | 0 |

| 8 | q1 | q1 | q5 | q5 |

| 1 | 1 | 0 | 0 |

| 10 | q2 | q3 | q5 | q5 |

| 1 | 1 | 0 | 0 |

| 11 | q3 | q3 | q4 | q5 |

| 1 | 1 | 0 | 0 |

| 12 | q3 | q3 | q5 | q5 |

| 1 | 1 | 0 | 0 |

Развязывание пар переходов в массиве М3

| 1 | q0 | q2 | q3 | q4 | |

| 0 | 1 | 1 | 0 | ||

| 0 | 1 | 1 | 1 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 2 | q0 | q2 | q4 | q4 | |

| 0 | 1 | 0 | 0 | ||

| 0 | 1 | 1 | 1 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 3 | q0 | q2 | q5 | q5 | |

| 0 | 1 | 0 | 0 | ||

| 0 | 1 | 0 | 0 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 4 | q1 | q2 | q3 | q4 | |

| 1 | 1 | 1 | 0 | ||

| 0 | 1 | 1 | 1 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 5 | q1 | q2 | q4 | q4 |

| 1 | 1 | 0 | 0 |

| 6 | q1 | q2 | q5 | q5 |

| 1 | 1 | 0 | 0 |

| 7 | q2 | q2 | q3 | q4 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 1 |

τ2 |

|

| 0 | 0 | 1 | 1 |

τ3 |

| 8 | q2 | q2 | q4 | q4 |

| 1 | 1 | 0 | 0 |

| 9 | q2 | q2 | q5 | q5 |

| 1 | 1 | 0 | 0 |

| 10 | q3 | q4 | q5 | q5 | |

| 1 | 0 | 0 | 0 | ||

| 1 | 1 | 0 | 0 |

τ2 |

| 11 | q4 | q4 | q5 | q5 | |

| 0 | 0 | 0 | 0 | ||

| 1 | 1 | 0 | 0 |

τ2 |

Таблицы состояний при кодировании пошагово

Iй шаг

|

τ1 |

τ2 |

|

| q0 | 0 | - |

| q1 | 1 | 0 |

| q2 | 1 | 1 |

| q3 | 1 | 1 |

| q4 | 0 | - |

| q5 | 0 | - |

IIй шаг

|

τ1 |

τ2 |

τ3 |

|

| q0 | 0 | 0 | - |

| q1 | 1 | 0 | 0 |

| q2 | 1 | 1 | 0 |

| q3 | 1 | 1 | 1 |

| q4 | 0 | 1 | 1 |

| q5 | 0 | 0 | - |

IIIй шаг

|

τ1 |

τ2 |

τ3 |

|

| q0 | 0 | 0 | 0 |

| q1 | 1 | 0 | 0 |

| q2 | 1 | 1 | 0 |

| q3 | 1 | 1 | 1 |

| q4 | 0 | 1 | 1 |

| q5 | 0 | 0 | 1 |

IVй шаг

|

τ1 |

τ2 |

τ3 |

|

| q0 | 0 | 0 | 0 |

| q1 | 1 | 0 | 0 |

| q2 | 1 | 1 | 0 |

| q3 | 1 | 1 | 1 |

| q4 | 0 | 1 | 1 |

| q5 | 0 | 0 | 1 |

Развязывание без τ1

Развязывание пар переходов в массиве М0

| 1 | q0 | q0 | q1 | q1 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 0 | 0 |

τ3 |

|

| 0 | 0 | 1 | 1 |

τ4 |

| 3 | q0 | q0 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 2 | q0 | q0 | q2 | q3 |

| 0 | 0 | 1 | 1 |

| 6 | q1 | q1 | q4 | q0 | |

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 1 | 0 |

τ3 |

|

| 1 | 1 | 0 | 0 |

τ4 |

| 4 | q1 | q1 | q2 | q3 |

| 0 | 0 | 1 | 1 |

| 5 | q1 | q1 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 7 | q1 | q1 | q5 | q0 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 |

τ3 |

|

| 1 | 1 | 0 | 0 |

τ4 |

| 8 | q2 | q3 | q4 | q0 | |

| 1 | 1 | 1 | 0 | ||

| 0 | 1 | 1 | 0 |

τ3 |

|

| 1 | 1 | 0 | 0 |

τ4 |

| 9 | q2 | q3 | q5 | q0 |

| 1 | 1 | 0 | 0 |

| 10 | q3 | q3 | q4 | q0 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 0 |

τ3 |

|

| 1 | 1 | 0 | 0 |

τ4 |

| 11 | q3 | q3 | q5 | q0 |

| 1 | 1 | 0 | 0 |

Развязывание пар переходов в массиве М1

| 1 | q0 | q0 | q1 | q2 | |

| 0 | 0 | 0 | 1 | ||

| 0 | 0 | 0 | 0 |

τ3 |

|

| 0 | 0 | 1 | 1 |

τ4 |

| 2 | q0 | q0 | q2 | q2 |

| 0 | 0 | 1 | 1 |

| 3 | q0 | q0 | q3 | q4 |

| 0 | 0 | 1 | 1 |

| 4 | q0 | q0 | q4 | q4 |

| 0 | 0 | 1 | 1 |

| 5 | q1 | q2 | q3 | q4 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 6 | q1 | q2 | q4 | q4 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 7 | q1 | q2 | q5 | q0 | |

| 0 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 0 |

τ3 |

|

| 1 | 1 | 0 | 0 |

τ4 |

| 8 | q2 | q2 | q3 | q4 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 1 |

τ3 |

|

| 0 | 0 | 1 | 1 |

τ4 |

| 9 | q2 | q2 | q4 | q4 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 10 | q2 | q2 | q5 | q0 |

| 1 | 1 | 0 | 0 |

| 11 | q3 | q4 | q5 | q0 |

| 1 | 1 | 0 | 0 |

| 12 | q4 | q4 | q5 | q0 |

| 1 | 1 | 0 | 0 |

Развязывание пар переходов в массиве М2

| 1 | q0 | q1 | q2 | q3 |

| 0 | 0 | 1 | 1 |

| 2 | q0 | q1 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 3 | q0 | q1 | q4 | q5 | |

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 4 | q0 | q1 | q5 | q5 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 5 | q1 | q1 | q2 | q3 |

| 0 | 0 | 1 | 1 |

| 6 | q1 | q1 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 7 | q1 | q1 | q4 | q5 | |

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 8 | q1 | q1 | q5 | q5 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 9 | q2 | q3 | q4 | q5 | |

| 1 | 1 | 1 | 0 | ||

| 0 | 1 | 1 | 1 |

τ3 |

|

| 1 | 1 | 0 | 0 |

τ4 |

| 11 | q3 | q3 | q4 | q5 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 1 |

τ3 |

|

| 1 | 1 | 0 | 0 |

τ4 |

| 10 | q2 | q3 | q5 | q5 |

| 1 | 1 | 0 | 0 |

| 12 | q3 | q3 | q5 | q5 |

| 1 | 1 | 0 | 0 |

Развязывание пар переходов в массиве М3

| 1 | q0 | q2 | q3 | q4 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 2 | q0 | q2 | q4 | q4 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 3 | q0 | q2 | q5 | q5 | |

| 0 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 4 | q1 | q2 | q3 | q4 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 5 | q1 | q2 | q4 | q4 | |

| 0 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 6 | q1 | q2 | q5 | q5 | |

| 0 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 7 | q2 | q2 | q3 | q4 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 8 | q2 | q2 | q4 | q4 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 1 |

τ3 |

| 9 | q2 | q2 | q5 | q5 |

| 1 | 1 | 0 | 0 |

|

τ2 |

τ3 |

τ4 |

|

| q0 | 0 | 0 | 0 |

| q1 | 0 | 0 | 1 |

| q2 | 1 | 0 | 1 |

| q3 | 1 | 1 | 1 |

| q4 | 1 | 1 | 0 |

| q5 | 0 | 1 | 0 |

| 11 | q4 | q4 | q5 | q5 |

| 1 | 1 | 0 | 0 |

| 10 | q3 | q4 | q5 | q5 |

| 1 | 1 | 0 | 0 |

Развязывание без τ2

Развязывание пар переходов в массиве М0

| 1 | q0 | q0 | q1 | q1 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ4 |

| 3 | q0 | q0 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 2 | q0 | q0 | q2 | q3 | |

| 0 | 0 | 0 | 1 | ||

| 0 | 0 | 1 | 1 |

τ4 |

| 4 | q1 | q1 | q2 | q3 | |

| 0 | 0 | 0 | 1 | ||

| 1 | 1 | 1 | 1 |

τ4 |

|

| 0 | 0 | 1 | 1 |

τ5 |

| 6 | q1 | q1 | q4 | q0 | |

| 0 | 0 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 5 | q1 | q1 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 7 | q1 | q1 | q5 | q0 | |

| 0 | 0 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 8 | q2 | q3 | q4 | q0 | |

| 0 | 1 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 9 | q2 | q3 | q5 | q0 | |

| 0 | 1 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 10 | q3 | q3 | q4 | q0 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 11 | q3 | q3 | q5 | q0 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

Развязывание пар переходов в массиве М1

| 1 | q0 | q0 | q1 | q2 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ4 |

| 2 | q0 | q0 | q2 | q2 | |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 1 |

τ4 |

| 3 | q0 | q0 | q3 | q4 |

| 0 | 0 | 1 | 1 |

| 4 | q0 | q0 | q4 | q4 |

| 0 | 0 | 1 | 1 |

| 5 | q1 | q2 | q3 | q4 |

| 0 | 0 | 1 | 1 |

| 6 | q1 | q2 | q4 | q4 |

| 1 | 1 | 0 | 0 |

| 7 | q1 | q2 | q5 | q0 | |

| 0 | 0 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 8 | q2 | q2 | q3 | q4 |

| 0 | 0 | 1 | 1 |

| 9 | q2 | q2 | q4 | q4 |

| 0 | 0 | 1 | 1 |

| 10 | q2 | q2 | q5 | q0 | |

| 0 | 0 | 1 | 0 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 11 | q3 | q4 | q5 | q0 | |

| 1 | 1 | 1 | 0 | ||

| 1 | 0 | 0 | 0 |

τ4 |

|

| 1 | 1 | 0 | 0 |

τ5 |

| 12 | q4 | q4 | q5 | q0 | |

| 1 | 1 | 1 | 0 | ||

| 0 | 0 | 0 | 0 |

τ4 |

|

| 1 | 1 | 0 | 0 |

τ5 |

Развязывание пар переходов в массиве М2

| 1 | q0 | q1 | q2 | q3 | |

| 0 | 0 | 0 | 1 | ||

| 0 | 1 | 1 | 1 |

τ4 |

|

| 0 | 0 | 1 | 1 |

τ5 |

| 2 | q0 | q1 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 3 | q0 | q1 | q4 | q5 |

| 0 | 0 | 1 | 1 |

| 4 | q0 | q1 | q5 | q5 |

| 0 | 0 | 1 | 1 |

| 5 | q1 | q1 | q2 | q3 | |

| 0 | 0 | 0 | 1 | ||

| 1 | 1 | 1 | 1 |

τ4 |

|

| 0 | 0 | 1 | 1 |

τ5 |

| 6 | q1 | q1 | q3 | q3 |

| 0 | 0 | 1 | 1 |

| 7 | q1 | q1 | q4 | q5 |

| 0 | 0 | 1 | 1 |

| 8 | q1 | q1 | q5 | q5 |

| 0 | 0 | 1 | 1 |

| 9 | q2 | q3 | q4 | q5 | |

| 0 | 1 | 1 | 1 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 10 | q2 | q3 | q5 | q5 | |

| 0 | 1 | 1 | 1 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 11 | q3 | q3 | q4 | q5 | |

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | 0 | 0 |

τ4 |

| 12 | q3 | q3 | q5 | q5 | |

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | 0 | 0 |

τ4 |

Развязывание пар переходов в массиве М3

| 1 | q0 | q2 | q3 | q4 |

| 0 | 0 | 1 | 1 |

| 2 | q0 | q2 | q4 | q4 |

| 0 | 0 | 1 | 1 |

| 3 | q0 | q2 | q5 | q5 |

| 0 | 0 | 1 | 1 |

| 4 | q1 | q2 | q3 | q4 |

| 0 | 0 | 1 | 1 |

| 5 | q1 | q2 | q4 | q4 |

| 0 | 0 | 1 | 1 |

| 6 | q1 | q2 | q5 | q5 |

| 0 | 0 | 1 | 1 |

| 7 | q2 | q2 | q3 | q4 |

| 0 | 0 | 1 | 1 |

| 8 | q2 | q2 | q4 | q4 |

| 0 | 0 | 1 | 1 |

| 9 | q2 | q2 | q5 | q5 |

| 0 | 0 | 1 | 1 |

| 10 | q3 | q4 | q5 | q5 | |

| 1 | 1 | 1 | 1 | ||

| 1 | 0 | 0 | 0 |

τ4 |

|

| 1 | 1 | 0 | 0 |

τ5 |

| 11 | q4 | q4 | q5 | q5 | |

| 1 | 1 | 1 | 1 | ||

| 0 | 0 | 0 | 0 |

τ4 |

|

| 1 | 1 | 0 | 0 |

τ5 |

Развязывание переходов без τ1, τ2, τ3 не уменьшает сложность. Получаем:

|

τ3 |

τ4 |

τ5 |

|

| q0 | 0 | 0 | 0 |

| q1 | 0 | 1 | 0 |

| q2 | 0 | 1 | 1 |

| q3 | 1 | 1 | 1 |

| q4 | 1 | 0 | 1 |

| q5 | 1 | 0 | 0 |

В дальнейшем используем исходную таблицу:

|

τ1 |

τ2 |

τ3 |

|

| q0 | 0 | 0 | 0 |

| q1 | 1 | 0 | 0 |

| q2 | 1 | 1 | 0 |

| q3 | 1 | 1 | 1 |

| q4 | 0 | 1 | 1 |

| q5 | 0 | 0 | 1 |

Таблица переходов структурного автомата:

| 000 | 100 | 110 | 111 | 011 | 001 | |

| 00 | 000 | 100 | 111 | 111 | 000 | 000 |

| 01 | 000 | 110 | 110 | 011 | 011 | 000 |

| 10 | 100 | 100 | 111 | 111 | 001 | 001 |

| 11 | 110 | 110 | 110 | 011 | 011 | 001 |

Таблица выходов структурного автомата:

| 000 | 100 | 110 | 111 | 011 | 001 | |

| 00 | 0 | 0 | 1 | 1 | 1 | 0 |

| 01 | 0 | 0 | 0 | 1 | 0 | 0 |

| 10 | 0 | 0 | 1 | 1 | 0 | 0 |

| 11 | 0 | 0 | 0 | 1 | 1 | 0 |

Формирование функций выходов и функций возбуждения памяти автомата

Таблица переходов RS-триггера

| S | R |

|

|

| 0 | 1 | ||

|

1 0 1 0 |

1 1 0 0 |

0 1 0 x |

1 1 0 x |

Функция входов RS-триггера Преобразованная функция входов

|

qисх |

S R |

qкон |

|

0 0 1 1 |

11 v 10 01 10 11 v 01 |

0 1 0 1 |

|

qисх |

S R |

qкон |

|

0 0 1 1 |

1 * 0 1 1 0 * 1 |

0 1 0 1 |

Функция возбуждения памяти автомата при синтезе на RS-триггерах

| 000 | 100 | 110 | 111 | 011 | 001 | |

| 00 | 1*1*1* | *11*1* | *1*101 | *1*1*1 | 1*1010 | 1*1*10 |

| 01 | 1*1*1* | *1011* | *1*11* | 10*1*1 | 1**1*1 | 1*1*10 |

| 10 | 011*1* | *11*1* | *1*101 | *1*1*1 | 1*10*1 | 1*1**1 |

| 11 | 01011* | *1011* | *1*11* | 10*1*1 | 1**1*1 | 1*1**1 |

Функция выходов y = f (x1, x2, τ1, τ2, τ3)

Функция возбуждения U = f (x1, x2, τ1, τ2, τ3) (S1, R1, S2, R2, S3, R3)

Таблица истинности функции выходов и функции возбуждения памяти конечного автомата.

|

x1 |

x2 |

τ1 |

τ2 |

τ3 |

y |

S1 |

R1 |

S2 |

R2 |

S3 |

R3 |

|

0 0 0 0 0 0 |

0 0 0 0 0 0 |

0 1 1 1 0 0 |

0 0 1 1 1 0 |

0 0 0 1 1 1 |

0 0 1 1 1 0 |

1 * * * 1 1 |

* 1 1 1 * * |

1 1 * * 1 1 |

* * 1 1 0 * |

1 1 0 * 1 1 |

* * 1 1 0 0 |

|

0 0 0 0 0 0 |

1 1 1 1 1 1 |

0 1 1 1 0 0 |

0 0 1 1 1 0 |

0 0 0 1 1 1 |

0 0 0 1 0 0 |

1 * * 1 1 1 |

* 1 1 0 * * |

1 0 * * * 1 |

* 1 1 1 1 * |

1 1 1 * * 1 |

* * * 1 1 0 |

|

1 1 1 1 1 1 |

0 0 0 0 0 0 |

0 1 1 1 0 0 |

0 0 1 1 1 0 |

0 0 0 1 1 1 |

0 0 1 1 0 0 |

0 * * * 1 1 |

1 1 1 1 * * |

1 1 * * 1 1 |

* * 1 1 0 * |

1 1 0 * * * |

* * 1 1 1 1 |

|

1 1 1 1 1 1 |

1 1 1 1 1 1 |

0 1 1 1 0 0 |

0 0 1 1 1 0 |

0 0 0 1 1 1 |

0 0 0 1 1 0 |

0 * * 1 1 1 |

1 1 1 0 * * |

0 0 * * * 1 |

1 1 1 1 1 * |

1 1 1 * * * |

* * * 1 1 1 |

|

|||||

|

|||||

* |

1 | 0 | * | * | 0 | 1 | * |

| 1 |

|

1 | 0 |

|

|

1 | 0 |

| 0 | * | * | 0 | 0 | * | * | 0 |

| 0 | 0 |

|

0 | 0 | 0 | 0 | 0 |

* |

* | * | * | * | * | * | * |

|

|

* | 1 | 1 | 1 | 1 | * | 1 |

| 1 | * | * | 1 | 1 | * | * | 1 |

| 1 | * | * | 1 | 0 | * | * | 0 |

y = τ1τ3 v x1x2τ2 v x2τ2τ3 v x1x2τ2τ3 S1 = x1 v τ3

* |

1 | 1 | * | * | 1 | 1 |

|

| * | 1 | 0 | * | * | 0 | 1 | * |

| * | * | * | * | * | * | * | * |

|

|

1 | 1 | * | 1 | 1 | 1 | 1 |

|

|

* | * |

|

* | * |

|

* |

|

|

* | * | * | * | * | * | 1 |

| 1 | * | * | 1 | 1 | * | * | 1 |

|

|

|

0 | 1 | 0 | 0 | 1 | 1 |

|

|

R1 = x2 v τ3 S2 = τ3 v x2 v τ1x1

|

|

* |

1 |

|

* | * | 1 | 1 | * |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

|

|

* | * | * | * | * | * | * |

| * | * | 1 | * | 1 | 1 | * | * |

* |

0 |

|

* | * | 1 | 0 | * |

|

|

* | * | * | * | * | * | * |

|

|

* | * | 1 | * | * | * | * |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

R2 = x2 v τ2 S3 = x2 v τ2 v τ3

* |

1 | * | * |

|

* | 1 | * |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | * | * | 0 | 1 | * | * | 1 |

| * | * |

|

* | * | * | * | * |

R3 = x1 v τ1 v x2τ2

Схема синтезированного конечного автомата

Выбор метода обеспечения контролепригодности

Для повышения контролепригодности разрабатываемого устройства можно предусмотреть ряд мер:

1) Обеспечение простоты начальной установки элементов памяти.

В схеме должна обеспечиваться возможность установки всех элементов в начальное состояние. Таким образом, в схеме должна присутствовать функция сброса (Reset)

2) Улучшения характеристик управляемости и наблюдаемости можно достичь за счет обеспечения доступа к ключевым точкам схемы.

Это достигается использованием элементов с тремя состояниями.

3) Наличие цепей обратной связи существенно усложняет процедуру генерации теста и моделирования неисправностей, поэтому нужно обеспечить возможность разрыва цепей обратной связи.

Преобразование схемы устройства для обеспечения контролепригодности.

Составление временной диаграммы работы

устройства, анализ правильности функционирования

Представим в оболочке OrCAD системы логических уравнений, полученных в результате минимизации.

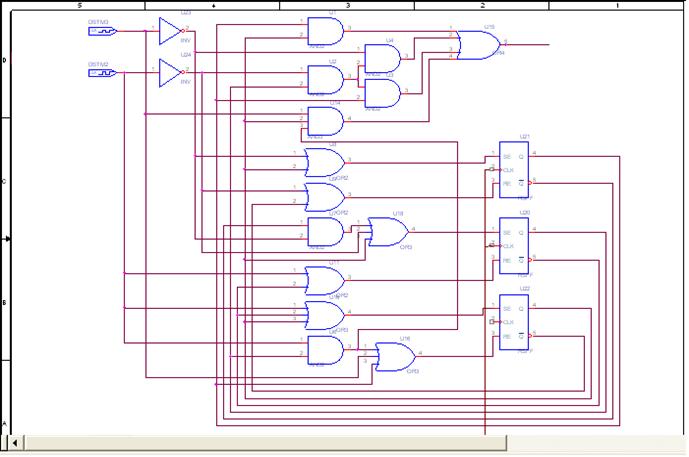

Полученная в

результате схема представлена на рисунке:

Полученная в

результате схема представлена на рисунке:

Схема автомата в оболочке OrCAD,

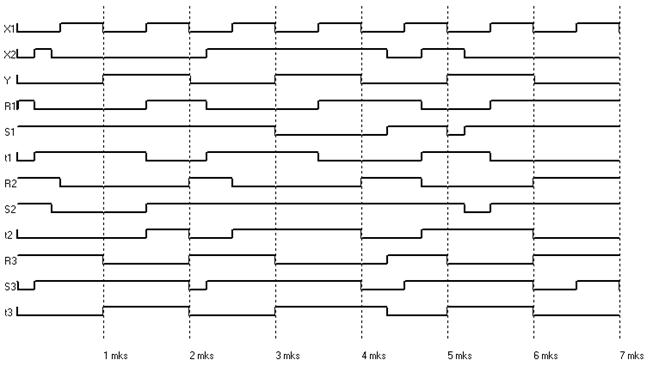

Временные диаграммы работы этой схемы приведены на следующем рисунке.(Низкий уровень – логический 0, высокий – логическая единица):

Временные диаграммы

По временным диаграммам видно, что смоделированная логическая схема функционирует правильно.

Разработка принципиальной схемы устройства

Основные параметры типовых ИС

|

Техно логия |

Тип | Серия | Параметр | |||

|

Рпот, мВт |

tр. тип, нс |

tр. макас, нс |

Эпот., пДж |

|||

|

Б и п о л я р н ы е |

ТТЛ (Si) быстродействующие |

130 К131 |

22 22 |

6 6 |

10 10 |

132 132 |

|

ТТЛ (Si) Стандартные |

К133 КМ133 К155 КМ155 |

10 10 10 10 |

10 10 10 10 |

22 22 22 22 |

100 100 100 100 |

|

|

ТТЛ (Si) Маломощные |

134 | 1 | 33 | 100 | 33 | |

|

ТТЛШ (Si) быстродействующие |

530 КР531 КМ531 |

19 19 19 |

3 3 3 |

5 5 5 |

57 57 57 |

|

|

ТТЛШ (Si) маломощные |

533 К555 КМ555 |

2 2 2 |

9,5 9,5 9,5 |

20 20 20 |

19 19 19 |

|

|

ТТЛШ (Si) быстродействующие усовершенствованные |

1531 КР1531 |

4 4 |

3 2 |

6 3,9 |

12 8 |

|

|

ТТЛШ (Si) маломощные усовершенствованные |

КР1533 | 1 | 4 | 11 | 4 | |

| ЭСЛ (Si) |

100 К500 К1500 |

25 25 40 |

2 2 0,75 |

2,9 2,9 0,75 |

50 50 30 |

|

|

Уни по ляр ные |

КМОП (Si) |

К561 564 1564 КР1554 |

0,0025 на 1 МГц |

45 45 10 3,5 |

200 200 45 17 |

0,1 0,1 0,025 0,008 |

| НОПТШ (GaAs) | К6500 | 3..6 | 0,1 | 0,42 | 0,3..0,6 | |

Примечания.

Рпот.- средняя потребляемая мощность.

tр. тип, tр. макас.- время задержки распространения сигнала типовое, максимальное.

Эпот.- потребление энергии на один бит информации (энергия переключения).

Допустимые параметры проектируемой схемы при реализации на ИС различных серий

| Серия ИС | Параметр | |

| Глубина схемы | Сложность схемы | |

| 130, К131 | 100 | 3 |

| К134 | 10 | 80 |

| К133, КМ133 | 45 | 8 |

| К155, КМ155 | 45 | 8 |

| К555, КМ555 | 20 | 40 |

| 533 | 20 | 40 |

| 530 | 200 | 4 |

| КР531, КМ531 | 200 | 4 |

| КР1533 | 90 | 80 |

| 1531 | 166 | 20 |

| КР1531 | 256 | 20 |

| 100, К500 | 344 | 3 |

| К1500 | 1333 | 2 |

| К561 | 5 | 32000 |

| 564, 1564 | 5 | 32000 |

| КР1554 | 58 | 32000 |

| К6500 | 2380 | 20 |

Анализ таблицы показывает, что из рассмотренных серий ИМ для реализации синтезируемого автомата могут быть использованы все серии, кроме 130, К131, 530, КР531, КМ531, 100, К500, К1500.

Выберем серии КР1531, 1531. Анализ полученных в процессе синтеза логических уравнений, а также допустимых параметров проектируемого устройства показывает, что использование ИС серии КР1531 является предпочтительным, поскольку обеспечивает меньшую потребляемую мощность при выполнении требований по быстродействию устройства. Кроме того, данная серия ИС обладает практически всей номенклатурой логических элементов, необходимой для реализации полученных в процессе синтеза логических уравнений. Для большего упрощения схемы применим также микросхемы серии К555, так как они также построены на ТТЛ.

Проверим возможность указанных серий ИС по условиям эксплуатации. Основные технические данные выбранных серий ИС, характеризующие их устойчивость к воздействию внешних факторов, приведены в таблице:

Допустимые значения внешних воздействующих факторов

| Наименование | Значение | |

|

КР1531 |

К555, К155 |

|

|

Синусоидальная вибрация: диапазон, частот, Гц амплитуда ускорения, м/с2 |

От 1 до 2000 200 |

От 1 до 5000 400 |

|

Механический удар одиночного действия: пиковое ударное ускорение, м/с2 длительность действия ударного ускорения, мс |

1500 0,1-0,2 |

15000 0,1-0,2 |

|

Механический удар многократного действия: пиковое ударное ускорение, м/с2 длительность действия ударного ускорения, мс |

1500 1-5 |

1500 1-5 |

|

Линейное ускорение, м/с2 |

5000 | 5000 |

|

Пониженная температура среды, 0С: рабочая Предельная |

-10 -60 |

-60 |

|

Повышенная температура среды, 0С: рабочая Предельная |

70 85 |

125 |

|

Изменения температуры среды, 0С |

от -65 до 85 | от -60 до 125 |

Сравнения приведенных характеристик с заданным в техническом задании условиями эксплуатации проектируемого устройства показывает, что любая из рассмотренных серий ИС может быть использована для его реализации.

Проверим возможность использования выбранных серий ИС по сроку эксплуатации. Характеристики надежности ИС приведены в таблице:

Характеристики надежности и сохраняемости ИС

| Серия ИС | Наработки на отказ, час | Срок сохраняемости, лет |

|

КР1531 |

50000 | 15 |

|

К555, К155 |

80000 | 15 |

Из приведенных характеристик видно, что по сроку сохраняемости ИС выбранных серий могут быть использованы для реализации проектируемого устройства.

Для реализации проектируемого устройства выберем следующие ИС:

К1531ЛР9 K555ЛИ

|

|||

|

|||

К1531ЛН1 К555ЛЛ1

|

|||

|

|||

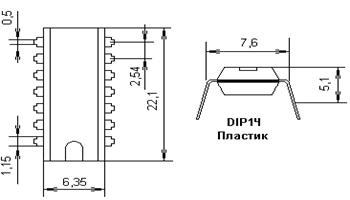

К155ТР2

По материалу изготовления (пластик), габаритам и количеству выводов (ножек -14) эти ИС абсолютно идентичны.

Питание подается на 14-ый вывод (14-ю ножку), а земля или логический ноль – на 7-ой вывод (ножку). Соединяем все незадействованные входы задействованных элементов параллельно с одним из задействованным входом, а все незадействованные входы незадействованных элементов – с землей (логическим нулём).

Чтобы исключить низкочастотные помехи, на печатных платах вблизи разъема устанавливают развязывающие конденсаторы. Для ТТЛ ИС их емкость обычно выбирается из расчета не менее 0.1 мкФ на одну ИС.

Для исключения ВЧ помех, развязывающие конденсаторы рекомендуется размещать по площади печатной платы из расчета один конденсатор на группу не более чем из 10 ИС. Для ТТЛ ИС их емкость обычно выбирается из расчета не мене 0.002 мкФ на одну ИС.

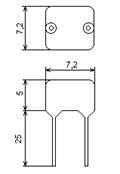

Выберем для установки на плате два конденсатора типа КМ-6-Н90-1.0мкФ и один конденсатор типа КМ-6-Н50-0.1мкФ

Конденсаторы КМ6

Поскольку суммарное количество входных, выходных шин и шин питания разрабатываемого устройства равно 5, выберем для установки на плате разъем типа ГРПМ-5Ш КЕО.364.194.ТУ

Расчет основных параметров устройства

Для оценки быстродействия необходимо определить пути распространения сигналов от входа к выходу максимальной глубины. Анализ схемы показывает, что такой путь:

И -> ИЛИ -> Т -> И -> И-> ИЛИ => 3И – 2ИЛИ – Т

Максимальное время переключения схемы при распространении сигнала по рассмотренному варианту пути составляет:

3*11+2*11+17=72 нс

Таким образом, максимальное время переключения синтезированной схемы не превышает 72 нс.

Потребляемая схемой мощность определяется исходя и характеристик ИС и вариантов их коммутации. Мощность составляет при этом:

4+8+2*4+2+4=26 мА

Интенсивность отказов устройства, содержащего разнотипные элементы, определяется следующим соотношением:

![]()

Среднее время наработки на отказ устройства составляет:

Tср = 1/λ

| № | Тип элемента | Число элементов Q | λ | Q*λ |

| 1 |

К1531ЛР9 К1531ЛН1 К1531ТВ10 К555ЛИ К555ЛЛ1 |

1 1 2 2 1 |

0.017*10-6 0.017*10-6 0.017*10-6 0.017*10-6 0.017*10-6 |

0.017*10-6 0.017*10-6 0.034*10-6 0.034*10-6 0.017*10-6 |

| 2 | Паяные соединения | 170 |

10-9 |

0.17*10-6 |

| 3 | Конденсаторы | 3 |

0.004*10-6 |

0.012*10-6 |

| 4 | Вилка разъема | 1 |

0.011*10-6 |

0.011*10-6 |

| Суммарная интенсивность отказов |

0.25*10-6 |

|||

Перечень комплектующих элементов устройства и значений интенсивности их отказов:

Время наработки на отказ разработанного устройства при этом составит:

Тотк=106/0.25=3846153 час

Оценка степени выполнения задания

| № | Параметр | Требование ТЗ | Полученное значение | Оценка степени выполнения |

| 1 | Время переключения | Не более 72 нс | <1 мкс | Выполнено |

| 2 | Потребляемая мощность | Не более 26 мВт | <80 мВт | Выполнено |

| 3 | Наработка на отказ | Не менее 65000 час | >3846153 час | Выполнено |

| 4 | Срок эксплуатации | 15 лет | ≥15 лет | Выполнено |

Литература

- Проектирование цифровых устройств. СПб, БГТУ 2000

- Интегральные микросхемы, справочник. М., Энергоатомиздат 1985

- Справочник по электрическим конденсаторам. М., Радио и связь 1983

- http://www.sitednl.narod.ru/1.zip - база сотовых по Петербургу

Q

Q 1

1 1

1 0

0 1

1 *

*

*

* 1

1 1

1 1

1 1

1 1

1 *

* *

*